Reducing PCB Costs through Panel Optimization

You think you’re buying boards, but you’re paying for panels.

When we consider ways to drive costs down for printed circuit boards (PCBs), it seems the first choice is to browbeat fabricators into submitting lower bids. That’s neither healthy nor right. Your technology partners need to be financially healthy.

If, instead, we look at material costs as a potential area for savings, we can find fertile ground for cost savings that an OEM can control.

Many OEMs consider panelization a manufacturing task and blindly delegate those decisions to suppliers, both fabrication and assembly. In doing so, they are missing an opportunity to affect material expenses, a leading cost driver for PCBs. Additionally, OEMs usually have multiple suppliers they work with: some for fabrication, others for assembly, and different ones for prototype versus production. Each supplier has its own panelization constraints and preferences. Thus, the communication process between OEM and each of its suppliers is repeated and inefficient, and little is done to maximize material utilization consistently across all suppliers. Ultimately, though, the OEM is responsible for product costs.

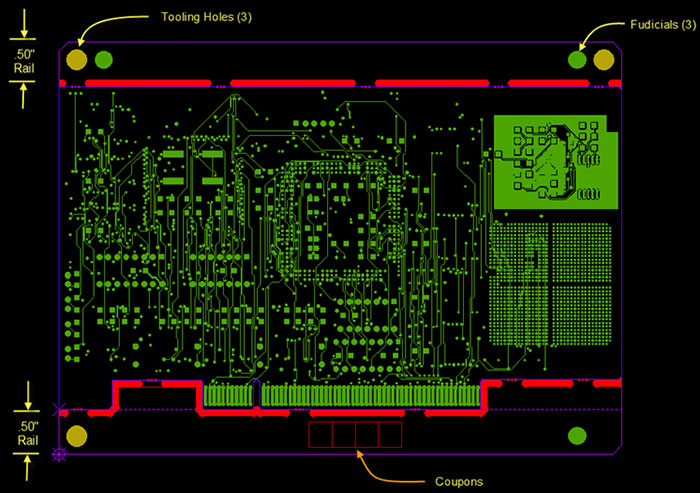

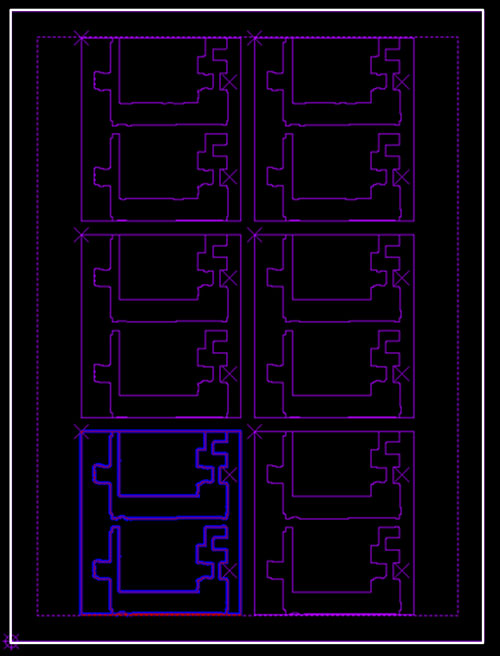

What’s a “panel?” Among OEMs and suppliers there can be confusion about what the term “panel” means. The assembly panel is the deliverable the OEM expects back from the fabricator (FIGURE 1). It is the product that will be put on the assembly line. It does not necessarily imply multiple PCBs within the array, although it often does. At a minimum, it includes the PCB, tooling holes, fiducials, and frequently at least one rail for the SMT line to use for transporting.

Figure 1. Assembly panel or array.

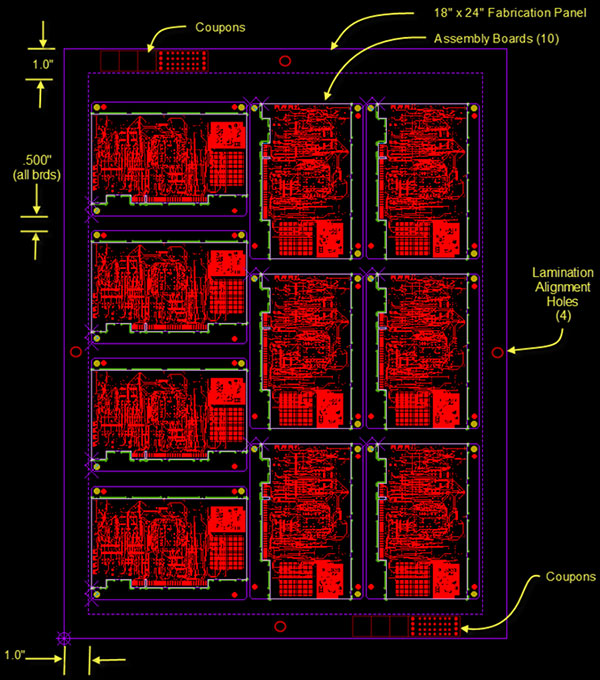

The fabrication panel (FIGURE 2) represents how the assembly panel will be configured while going through the fabrication process. It almost always entails a stepped-and-repeated image of the assembly panel onto a panel size the fabricator uses. The fabrication panel will most certainly contain other features, such as coupons, nomenclature, venting, and thieving patterns, as well as their own tooling holes. While the fabrication panel configuration is ultimately the fabricator’s responsibility, knowing how the assembly panel will fit within a fabricator’s panel provides insight into the potential cost of the assembly panel.

Figure 2. Fabrication panel.

Costs reducers. There is also a tendency to dismiss the significance of material costs during prototyping because the number of panels needed is usually quite small. The objective is to get a small number of functioning boards to test. The costs that drive prototyping are affected mostly by the delivery required, whether the design has constrained nets, and the types of material and finish required. But often, once the prototypes are successful, the same PCB and the same assembly panel are assumed to be acceptable for production. Acceptable and optimized are not the same, however.

Additionally, there are significant inefficiencies in the design-to-manufacturing (DfM) release process when it comes to panels. The typical flow is for the OEMs to use guidelines provided by their assembler as input in drawing their assembly panel layout. These guidelines are documents that are interpreted by each person doing the assembly panel drawing and then created using an application different from the one used to design the PCB.

Finally, it is sent as a drawing file to the fabricator. The fabricator then interprets the drawing file and reenters the configuration in its CAM system, generating a checkplot to be sent back to the OEM for validation before proceeding to tool for production. Only then does the OEM know how many panels are going to be needed for the build, as well as their costs. That’s a lot of wasted resources on something that’s not complicated.

Instead, an OEM should consider incorporating the assembly and fabrication suppliers’ panel guidelines into a software tool that removes the risk of interpretation and the redundancies of recreating each time. A real benefit is the early visibility the OEM has on cost effects of the material for the design and assembly panel. This empowers consideration of alternative layouts of the assembly panel to lower the material costs.

With this early visibility, some high-volume OEMs will even want to evaluate changes to the PCB profile if it will give them greater material utilization in production. For example, a PCB designer for a mobile-communications OEM was able to increase material utilization to 88% from 52% by redefining a board feature that permitted interlocking the PCBs in a panel.

Preventing problems. For panelization software to fully benefit the process, it must be able to do all the tasks required. This provides full visibility of the true cost-saving opportunities. For example, it should be able to do the following:

- Store panel guidelines of all fabrication and assembly partners.

- Quickly and easily create panels optimized for both assembly and fabrication.

- Consider panel size, rail widths, margins, moat width, number of boards and component overhang.

- Perform actions including pattern filling, addition of tooling holes, fiducials, bad board marks, targets, text, barcode, breaktabs, v-score lines, and rout.

- Calculate exact material utilization to identify cost impact.

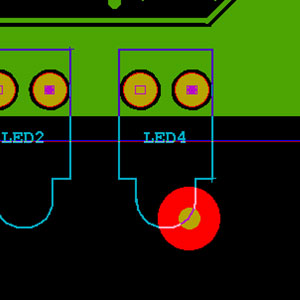

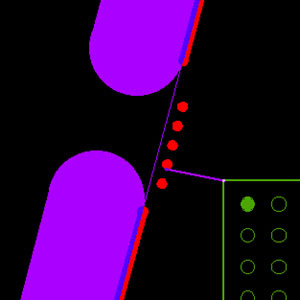

Also, what steps were taken to ensure the assembly panel configuration did not introduce its own manufacturing issues? Many issues in an assembly panel can be created unbeknownst to the designer, only to have the fabricator report back it cannot build it as designed. Even worse, some of these issues might not manifest until the assembly panels reach the assembly operation, making it a costly mistake. DfM software can be used to systematically check for assembly panel issues. FIGURES 3 to 5 are examples of manufacturing issues often introduced by the assembly panel.

Figure 3. Component too close to conveyed edge risks damage.

Figure 4. LED obstructing access to fiducial prevents proper registration.

Figure 5. Breakaway tab too close to SMD pad causes stress on the pad when separating.

A side benefit of taking control of panelization is the OEM can view each supplier’s requirements and be assured the output sent is not only acceptable, but optimized for the OEM’s objectives. This process will also prevent the inefficiency stemming from communicating and resolving the same topics with each supplier. This consistency is further enabled by sending the panel data as part of the intelligent data transfer container provided them, instead of as a drawing file.

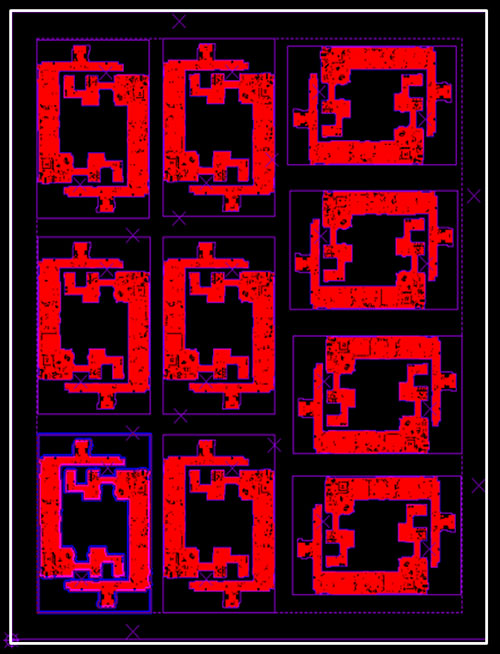

Materials savings. Consider material utilization percentages. Fabricators provide a number that is usually impressively high, say above 60%. It sounds good, but is deceiving. The fabricator is stating how much of the fabrication panel is used based on the assembly panel provided them. The assembly panel is always a rectangular box that fits into rectangular panels nicely.

In reality, what the OEM cares about is the actual material area used for the PCBs, not the assembly panel, because that determines how many panels need to be built for the order. As illustrated in FIGURE 6, the fabricator will report this material utilization at 58.9%, but because of the shape of this PCB, the actual material utilization is only 18.7%.

Figure 6. Fabricators see this as 58.9% material utilization, whereas an OEM sees this as 18.7% actual material utilization based on the PCB.

We studied four different designs, each with its own definition of production volume, to measure the potential material savings to an OEM. PCB 1 is a rigid PCB built in lot sizes of up to 2,000. FIGURE 7 illustrates that before panel optimization, the OEM was getting 18.7% material utilization on an 18 x 24" fabrication panel, with two PCBs per array and six arrays per panel. When the OEM optimized its assembly panel, it found it could get 31.5% material utilization, yielding 10 arrays of two PCBs per fabrication panel. The panel optimization software automatically nested circuits into a tighter assembly panel in spite of its nonstandard shape.

Figure 7. Optimized assembly within an optimized fabrication panel.

We then applied the results to a simple costing spreadsheet that considered:

- Number of PCBs ordered.

- Fabrication panel square area.

- Fabrication panel cost/sq. in.

- Fabrication panel overage needed (to accommodate scrap).

The fabrication panel overage is a variable because lower percentages are required with higher volume. All other variables were considered to be constant between the two scenarios.

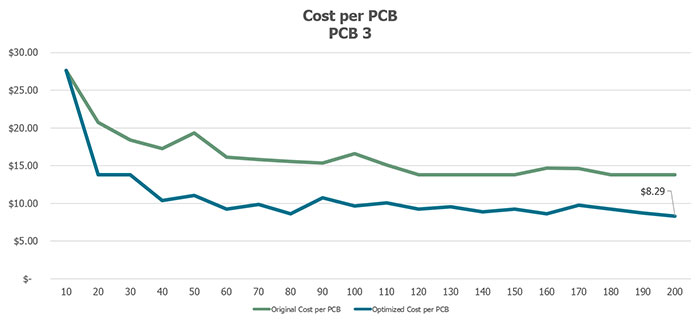

For the first example, we calculated the costs before and after panel optimization for order sizes between 100 and 2,000, in increments of 100.

As shown in FIGURE 8, in all volumes, the optimized panel showed significant cost savings. Further, we identified the order size that yielded the lowest cost per PCB. Would you change an order size if you knew where the lowest possible cost per PCB was?

Figure 8. For all volumes, the optimized panel showed significant cost savings.

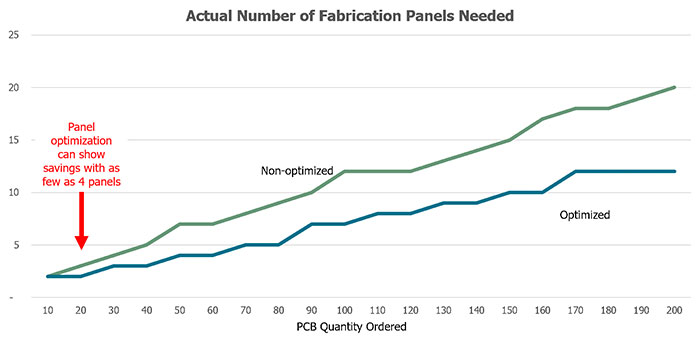

FIGURE 9 shows the actual number of fabrication panels needed, non-optimized and optimized. While it might initially be surprising that these lines are not entirely straight, they reflect the combination of variables previously stated. What may be even more surprising is that panel optimization can show cost savings in as few as four panels for this design.

Figure 9. Actual number of fabrication panels needed, non-optimized and optimized.

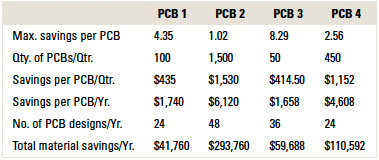

Last, over a test sample of four PCBs, again each with their own production volume, there are impressive savings across the board, even when only a small number of PCBs are designed each year (TABLE 1).

Table 1. Cost Savings for the 4 Example PCB Panels

As a bonus, when considering labor costs involved to define, create and communicate all the panelization instructions, a systematic panelization tool also can have meaningful labor savings.

is market development manager at Mentor; patrick_mcgoff@mentor.com.