Current Issue

New Requirements for SIR Measurement

Requirements for no-clean solder paste to increase device chemical, thermal and electrical reliability.

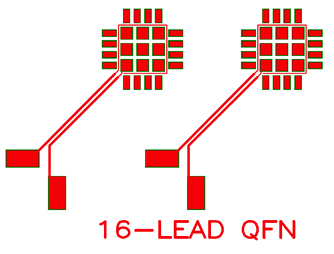

Since the beginning of surface mount technology, many measurement methods have been created to qualify the quality/stability of flux residues with solder paste. This means there are international, national and company standards for qualification of the auxiliary material.1-6 Qualification gives an initial idea of the quality, but unfortunately does not provide all the information needed for the entire assembly. As an example, in some cases conformal coating will be applied over no-clean flux residues. Each single material could pass the qualification according to the standards, but in combination it is possible to create failures.7 Other areas include new types of (miniaturized) components, which could cause the physics to change, or even the end-use application: for instance, power devices in combination with surface mount on PCBs as in FIGURE 1. These types of components (QFNs/BTCs) are classical SMD with voltages from 250V to 500V. Therefore, the physics could change due to the new component as well as new voltages, which creates a new quality/quantity of electrical field strength. A third area is the combination of high humidity and voltage. There are also requirements in the automotive industry for these devices.

Figure 1. Example of a power-QFN/BTC component.

Flux Penetration Under Components

Standard test methods for measuring effects of fluxes are the determination of insulation resistance only on free surfaces. In practice, electronics assemblies are considerably more complex. Among and between components, flux and dew moisture are concentrated. Depending on gap height and areas of the components, capillary forces can be affected differently. Certain component designs, such as QFN/BTC or LGA, make these effects more relevant. Even assembly cleaning is complicated by these small gaps. Indeed, perhaps this problem will intensify by cleaning.

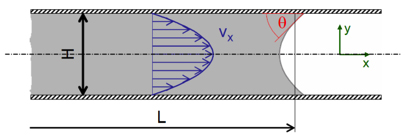

For a theoretical analysis of these phenomena, at first the condition on the resulting capillary gap should be considered. For this purpose, some similarities to the application of the known underfilling in flip-chip technology can be pointed to. There is a horizontal gap between parallel plates, which will be filled by a fluid, as has been simulated in the work of Haeussermann.8

Figure 2. Two-plate model (horizontal plates).8

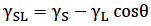

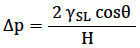

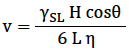

Starting from these geometrical conditions, the following equations (1) to (4) can be used for calculating the wetting by a liquid medium:

(1)

(1)

(2)

(2)

(3)

(3)

(4)

(4)

Instead of the underfill used in the original calculation, corresponding data for fluxes and PCB substrates could be sought. TABLE 1 shows the material properties used for this calculation, which is intended only as a typical example for illustration. As a substrate, a solder resist was assumed, whose surface energy is mainly dispersed,9 as is also the case for most organic solvents of the flux.

Table 1. Material Properties from Various References (Typical Examples)

| Material | Properties | Ref. | |

| Substrate |

Surface energy

|

39 mN/m | 10 |

| Contact angle (flux/mask) | 26.2° | ||

| Alcohol-based flux | Surface tension | 22.6 mN/m | 11 |

| Viscosity | 2.97 mPa*s | ||

| Flux cleaner | Surface tension | 23 mN/m | 12 |

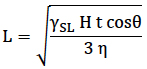

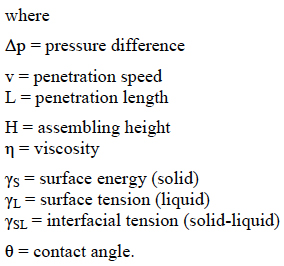

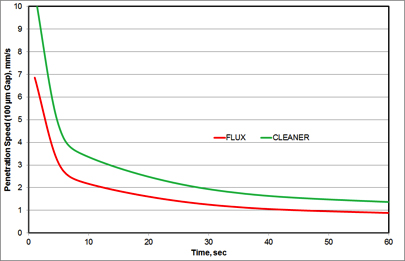

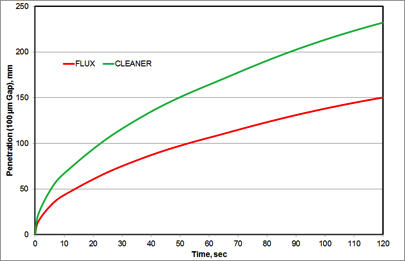

With the sample data, some estimation for wetting of the capillary gaps can be made. First, it can be calculated that the capillary filling pressure increases enormously with a decreasing gap. When gap heights are at 100µms and more, the pressure hardly changes with <5 mbar. For gaps smaller than 50µm, it increases drastically, e.g., up to 67 mbar for 5µm (FIGURE 3). However, very low pressures are sufficient to fill the gap completely with flux (in theory), because there is no opposing weight force in the horizontal position. The calculated depth of flux penetration in Figure 3 is calculated for a propagation time of one sec. The penetration depth increases with larger gap sizes, despite the smaller capillary pressure, which is mainly determined by the viscosity and resulting flow speed. FIGURE 4 shows the calculated penetration speeds in a 100µm gap for a flux and a cleaning agent, where the cleaning agent is wetting a little faster. The wetting rate is particularly high in the first 5 sec. and then approaches a lower limit of about 1mm/s.

Figure 3. Capillary pressure and penetration depth of the flux.

Figure 4. Dynamics for penetration for a flux and a cleaning agent.

Accordingly, flux penetration slows; however, the flux already has spread out nearly 50mm (in theory) after 10 sec. (FIGURE 5). For real components, complete filling of the gap may be achieved, in most cases, after the first second.

Figure 5. Penetration length depending on time.

The temperature was not taken into consideration in the shown calculations, which obviously also influences the wetting. Reviewing work from previous measurements,10 flux viscosity decreases as temperatures increase from 25° to 80°C by three to four orders of magnitude. The wetting or filling of the capillaries could be much faster. However, at these temperatures the solvent of the flux starts to evaporate, so that the flux dries, and the wetting process could stop. Since these are two competing mechanisms, the influence of temperature must be further investigated experimentally for selected fluxes.

Practical Investigation with QFN/BTC Components

A short test was developed to see the interaction of different combinations:

- Comparison of two no-clean (nc) vs. water washable (ww) solder pastes (Type 5 paste).

- Cleaning with solvent cleaner versus DI water.

- Two stencil thicknesses 20µm and 100µm.

A special board layout was created for a QFN/BTC with 16 leads (FIGURE 6).

Figure 6. QFN/BTC test structure.

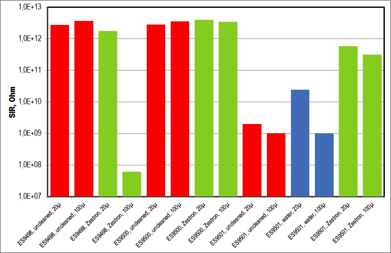

The potential difference came via the heat sink structure as negative (the component finish had 100% metal) and an additional wire where the PCB was located under the QFN body. A voltage of 50V was applied across a distance of 200µm between wire and pad. This generated a high field strength of 250 kV/m. FIGURE 7 shows the measured results after seven days (168 hr.) of high humidity and temperature at 85°C/85% RH, according to typical automotive requirements.

Generally the water wash paste t gave good results by using the solvent cleaner and worse results with the higher solder paste print deposit. The same happened with one of the no-clean fluxes. Due to the fact that these are just first results, it has to be verified with more samples and combinations.

Figure 7. SIR results with different combination.

High voltage investigation with an SIR comb. As mentioned, new components with high voltages are assembled on PCBs, and there is no field data on the interactions with solder paste flux residues. A short practical test was performed using the standard SIR comb with a test voltage of 1000V, which works well for dry conditions. After storage for seven days under high humidity and a temperature of 85°C/85% RH, the test was repeated and showed only single small variances of one magnitude, despite the presence of the solder paste (TABLE 2). For future investigations, a combination of actual component layouts and high-voltage measurements of the assembled test PCBs would be planned.

Table 2. SIR Results of 3 Different Solder Pastes with 1000V Applied Test Voltage

| PCB | A | B | C | D |

| Paste 1 | 376 E9 | 603 E9 | 186 E9 | 639 E9 |

| Paste 2 | 837 E9 | 608 E9 | 245 E9 | 48.5 E9 |

| Paste 3 | 447 E9 | 723 E9 | 471 E9 | 608 E9 |

| Initial PCB | 677 E9 | 496 E9 | 665 E9 | 602 E9 |

Investigation of Bedewing Effects

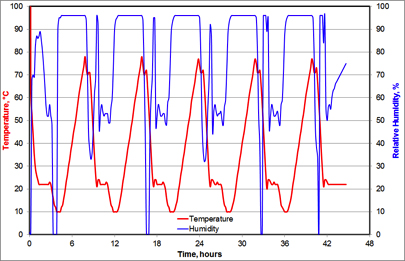

Electronic components exposed to large temperature differences can be particularly stressed by bedewing. If the environment cools quickly and a free exchange of air is also not possible, the water absorption capacity of the air decreases rapidly, and the excess water condenses. This phenomenon occurs, for example, in electronic appliances for automobiles, which must be specifically inspected and protected for this occurrence. FIGURE 8 shows the climatic conditions for such bedewing tests with five cycles between 10° and 80°C and a humidity of up to 90% RH. At the soaking temperature around 22°C, dewing starts.

Figure 8. Humidity and temperature during the bedewing test.

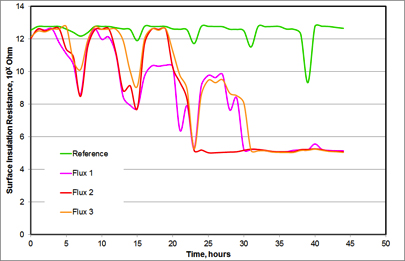

The electrical insulation resistance of conventional SIR comb structures can be measured by such a bedewing test. FIGURE 9 shows that even for a reference board without any ionic impurities, the insulation resistance may decrease by bedewing up to three orders of magnitude, from 1013 to 1010Ω. However, the insulation resistance is recovered after each drying phase.

Figure 9. Surface insulation (SIR) during the bedewing test.

This is completely different for flux contaminated printed circuit boards, especially if they are in operation under electrical voltage. The resistance drops down by hundreds of kiloohms and finally reaches an extremely low level. This is obviously a continuous short circuit caused by migration of ions. It can also be seen that the condition worsens gradually for each bedewing cycle, indicating a gradual propagation of conductive structures.

The used comb boards have the opportunity to dry out at every heating cycle relatively quickly. Actual assemblies can be even more critical, as among and between components, air circulation is not ensured and flux residues are especially concentrated in these areas. This issue will be the subject of follow-on work.

Conclusions and Further Work

Different single tests were addressed for understanding the new requirements for electrical and environmental properties on electrical devices. To make it easier and practical for future qualifications, a multifunctional project should be started that includes experts and users to discuss the various single influences.

This article was first published in the SMTA International Proceedings, October 2013, and is reprinted here with permission of the authors.

References

- ISO 9454-1 (DIN EN 29454-1)

- Bellcore GR-78-CORE

- Siemens Standard (SN 59650:1998)

- DIN 32513, Soft Soldering Pastes.

- IEC 61190, Electronic Assembly Materials.

- JIS Z 3197, Testing Methods for Soldering Fluxes.

- W. Schmitt, “Kompatibilität von bleifreien Lotpasten mit der Schutzlackierung,“ June 2006.

- Tanja Haeussermann, Simulation des Underfill-Prozesses bei Flip Chip-Anwendungen (Simulation of Underfilling Process for Flip-Chip Application), doctorial thesis, University Stuttgart, 2009.

- Hans Bell and Reiner Zajitschek, “Ergebnisse und Stand der Untersuchungen zum Lotperlenproblem” (“Results and Status of Investigation about Solder Ball Issues”), Berlin/Steinheim, 1994.

- Jinlin Wang, “The Effect of Flux Residue and Substrate Wettability on Underfill Flow Process in Flip Chip Packages,” IEEE 56th Electronic Components and Technology Conference, January 2006.

- Eli Westerlaken, “Performing Flux-Technology for Pb-Free SN100C Solders,” IPC Apex Expo Proceedings, March 2008.

- CRC Industries France S.A., Soldering Flux Cleaner – Technical Data Sheet, Argenteuil Cedex, 2004.

JOERG TRODLER is area/technology manager at Heraeus Materials Technology (heraeus.com); joerg.trodler@heraeus.com. is chair, Reliability and Safety Electronic Systems, at the University of Rostock (igs.uni-rostock.de); mathias.nowottnick@uni-rostock.de.

Press Releases

- Aven Welcomes Max Ramos to Strengthen Distribution Partner Operations

- ubersmt Expands SMT Line with Juki G-Titan Printer and RS-1R Placement System

- Keiron Technologies to Host LiFT Webinar Focusing on Solving Solder Paste Printing Challenges

- Express Manufacturing, Inc. Strengthens Test Capability with Acculogic Flying Probe System