The iPad will please makers of PoP, WLP and underfill. (Users, too.)

My iPad arrived today. It was exciting just opening the box. While this is the WiFi version, I can’t wait to see the 3G models. The display is awesome. It is very light, and I can see how it would be nice to carry. The virtual keyboard makes a sound when I type and is really easy to use. I will enjoy watching movies and reading magazines on an airplane, especially with the long battery life promised. What I really want to do is mount my iPad on the dash of my Prius, so I can use the map feature with the really cool touch display. Maybe I won’t get lost so often.

My iPad arrived today. It was exciting just opening the box. While this is the WiFi version, I can’t wait to see the 3G models. The display is awesome. It is very light, and I can see how it would be nice to carry. The virtual keyboard makes a sound when I type and is really easy to use. I will enjoy watching movies and reading magazines on an airplane, especially with the long battery life promised. What I really want to do is mount my iPad on the dash of my Prius, so I can use the map feature with the really cool touch display. Maybe I won’t get lost so often.

I did not look inside, but that was not necessary because almost every news article had a teardown analysis. It is really not the hardware that makes this product, but rather the user interface.

Inside the iPad. The A4 processor is believed to be an ARM processor and was probably designed by P.A. Semi, a fabless semiconductor company that Apple acquired in April 2008. Some analysts report the processor has a 1 GHz processing speed and is expected to be under clocked at 850 MHz to improve battery life.

Apple seems to be using the same packages as its other products. My iPad contains a package-on-package (PoP). My iPhone also contains a PoP, as does the iPod shuffle and my daughter’s iPod Touch.

The iPad has a few wafer-level packages (WLPs). A Broadcom WLP can be seen on one of the smaller boards. iFixit reports it is a 802.11n WiFi plus Bluetooth device.1 An Apple marking on a WLP may have been provided by Cirrus Logic. Other WLPs are peeking out from under the shielding. Several FBGAs (laminate CSP) are also clearly visible in the growing number of product teardowns surfacing on the Web.

The largest single product category for WLPs is mobile phones, with many handset makers using the package because of its small form factor and low profile. Apple uses WLPs in many products. One version of Apple’s iPhone contained WLPs from Marvell and CSR. The iPod shuffle also contained a WLP. TPSS, the Japanese teardown analyst organization, reported the iPhone 3G released in July 2008 contained several WLPs, including two in a Murata module, and WLPs from Maxim Integrated Products and Infineon.

PoP is growing in popularity for many portable products. Today’s applications for PoPs include mobile phones (the largest), digital cameras, MP3 players, and now the iPad. Future applications for PoP include medical product and laptop computers.

Apple likes to use PoP for its products. Last year, Nikkei Electronics reported the use of a PoP from Samsung in its teardown of a third-generation iPod shuffle.2 TPSS reported that the bottom package of the PoP for the iPod Touch containing the ARM processor had an 11 x 12 mm body size with a 0.65 mm thickness and 331 solder balls with 0.5 mm pitch. The top memory package contained one SDRAM with the same body size as the bottom package, but was slightly thinner, with a thickness of only 0.5 mm. The top package had 102 solder balls with 0.5 mm pitch.

Demand for PoP is driven by integration and miniaturization, business and logistics advantages, and requirements for standard and efficient interfaces for the high-speed bus between the processor and memory. TechSearch International estimates that more than 220 million PoPs shipped in 2009, and the volumes will continue to grow.3

Die stacking still popular. Many of Apple’s products continue to include stacked die. The top package of the PoP contains two stacked die (we assume memory). TPSS also reported several stacked die packages in Apple’s iPhone 3GS, including one with flip chip on the bottom. Many other stacked die packages used wire bond only. With the increased use of stacked die CSPs, it is no wonder billions of units are shipped each year.

It looks like there is plenty of underfill for the CSPs in the iPad, following the tradition Apple has used for its iPods and iPhones. This is good for me, because I have a habit of dropping everything. So far, our iPods, iPhones, and iTouch are still working. I know that the package suppliers say underfill is not required, but I am glad it is there.

It’s not just the introduction of the iPad that is so interesting, but the introduction of a new tablet format. While tablet PCs have been introduced in the past, the iPad may have the same impact as the introduction of the touch screen for smartphones. We are entering a new era in consumer products at a time when the industry needs excitement to drive unit volumes higher.

Computers, phones and now the iPad. What’s next for Apple? i3DTV?

References

1. www.ifixit.com/Teardown/iPad-Teardown/2183/3.

2. Nikkei Electronics, “3G iPod Shuffle Teardown, SoC, Flash Memory Stacked [Part 4],” April 6, 2009.

3. E. Jan Vardaman, “Semiconductor Packaging Expands in the Third Dimension,” MEPTEC Report, vol. 14, no. 1, Spring 2010.

E. Jan Vardaman is president of TechSearch International (techsearchinc.com); jan@techsearchinc.com. Her column appears bimonthly.

Printed electronics offer the best chance for a process revolution.

The printed circuit board process has been around since before the start of WWI and has only been improved upon since the conception of etched copper traces on a single-sided substrate. Significant improvements since include:

- Etching both sides and interconnect with eyelets, realizing twice the interconnect capability.

- Introduction of the plated through-hole, eliminating the eyelets.

- Multiple layer (multilayer) construction, creating several etched inner cores, laminated with presses, then forming PTH interconnections.

- SMOBC: Solder mask over bare copper, eliminating reflow of the SnPb, allowing smaller traces.

- SMT (surface mount technology).

A multitude of packaging techniques: Buried vias, where innerlayers are interconnected with PTHs; BGAs; blind vias, where small holes are laser-formed for interconnections, etc.

All these refinements were evolutionary, as none eliminated the basic principles of chemical etching and metal finishing. Indeed, some other “improvements” have simply complicated the manufacturing process to the point where yields become a big factor. In many high-tech boards, it’s really hit-and-miss, sorting the good from the bad.

With printed electronic circuits (PEC), however, the product is reduced to four simple, repeatable steps. At every fourth step, the product can be tested and reworked, eliminating the huge scrap of the old methods. Removing complexity reduces the capital investment required by up to 80%, yet the process should be considered “green” because it eliminates the PTH. Thus, the end-product should prove much more reliable, as the interconnect is a solid metal plug instead of a thin layer of copper plating.

Applications range from the most “impossible” designs to their simplest print-only counterparts, starting from RFID to forming a circuit trace on a hypodermic needle probe. Sub-mil lines with equal spaces, and buried and blind via formation, can be accomplished with nothing more than a silkscreen press.

As packaging density increases, the potential for more reliable end-products increases, with bonuses for economic and environmental benefits. Therefore, PEC may very well become the next-generation interconnect packaging method of choice for a very large portion of electronics. Existing PCB manufacturers must get on board, lest a new startup overtake the interconnect market.

With the demise of captive PCB operations, board manufacturers that doubled as technology developers have diminished. These were the board makers that at one time pushed the PCB fabrication envelope by introducing new processes and increasing reliability. Not much remains of those players today, and those left are converters. This is sad because innovation isn’t coming from the board shops, but rather from (sometimes outlandish) customer requirements, with board shops in turn struggling to make the product. Innovations in printed electronics now involve product designers, not the layout guys, and the process is very simple.

Basic conductive inks now are available. These include a low resistance silver (4x resistance of copper) and an LPI (photoimageable dielectric), which have produced 0.001˝ with UV exposers and sub-mil lines should be possible with LDI equipment. Silver conductive ink for now will satisfy commercial needs, and we expect that R&D efforts worldwide at the university level, as well as commercial alliances, will eventually lead to a conductive nanoparticle copper ink.

Traditional PCB processes require many consumable products. For example, a drill bit might make 3,000 holes, so to build a common 25,000-hole PCB requires eight bits, at a rough cost of $16. Much chemistry is used and must be disposed of, such as dry film, excess copper and tin, plastic sheeting, release films, press pads, router bits, and so on.

By comparison, whatever is used in the PEC process remains on the board. While inks are more expensive than those used in the PCB process, the overall costs are less because a multitude of activity-based requirements are eliminated, not to mention the floor area and related costs (HVAC, lighting, etc.), power requirements to heat and cool the multiple processes, and on and on.

The PEC process is reworkable in every step, so there is no scrap. The old process banks on (the hope for) integrity of the inner traces, such as plated-hole formation, to be completely perfect until final testing is performed. In fact, a bad board is built alongside a good one, and that is a waste of money.

At the end-user level, board reliability could be improved because there is no weakness in solid metal via formation. PTH reliability, on the other hand, worsens as holes become smaller and metallization gets more difficult. With the advent of cooler solders and conductive adhesives, PEC stands to be a better product.

Is it 100% ready? Certain suppliers provide materials and process from which product can be made for evaluation purposes for the more complex assemblies. Other less-critical applications where the process can be applied abound.

Is this the beginning of the end for SMT? The answer is probably “yes,” although the timeline is undetermined.

Au.: My thanks to Mike DuBois of Caledon Controls for much of the content of this article.

Randall Sherman is president and CEO of New Venture Research Corp. (newventureresearch.com); rsherman@newventureresearch.com.

Five-and-a-half million: That’s how many light bulbs are purchased each day in the US. And yet, the market for incandescent bulbs is about to burn out. In fact, in Australia legislators have banned light bulbs, and the EU will switch off incandescent and halogen bulbs between 2009 and 2012. The mighty 100W bulb went out last year, and the 60W and 75W versions are next. In the US, the laws against incandescent kick in by 2012. (Halogen isn’t targeted.)

Five-and-a-half million: That’s how many light bulbs are purchased each day in the US. And yet, the market for incandescent bulbs is about to burn out. In fact, in Australia legislators have banned light bulbs, and the EU will switch off incandescent and halogen bulbs between 2009 and 2012. The mighty 100W bulb went out last year, and the 60W and 75W versions are next. In the US, the laws against incandescent kick in by 2012. (Halogen isn’t targeted.)

This throws open the door to a huge new market for fabricators and contract assemblers, but there are key differences from traditional SMT boards. In solid-state lighting, for instance, the LED and driver boards are separate, and the typical substrate for the former is metal core, not FR-4.

Thermal management, as our cover story last month detailed, is emphasized. While LEDs don’t throw as much heat as incandescent bulbs, there are still certain thermal issues to contend with. Most solid-state players try to design units that operate under a certain temperature to maximize output. “For an LED board, we look for a certain temperature at the joint,” says Scott Mauldin, director of operations of LEDnovation, a maker of LED lamps and luminaires. “This permits LEDs to get more lumens per watt” (of input).

LED parts for placement typically come on reels and can be put down by almost any decent placement machine. But there are advantages to be had: Smart feeders have a leg up, says Mauldin. Solid-state light manufacturers are interested in bin codes (which define the light characteristics of the LED). Bin codes might be mixed on a board to get the right amount of emitted light, which means assemblers must keep the bins separate.

In soldering, the thermal profile is very different than SMT parts. LEDs are sensitive to high heat. And rework is treacherous, as it is fairly difficult to heat up a single solder joint on a metal core board. (Some use hot plates for rework.)

A company like LEDnovation outsources assembly, emphasizing those with production experience with metal core boards, which eliminates about 80% of EMS companies today. That will need to change.

Mauldin is among the speakers at SMTA International’s EMS Forum this year. It’s definitely worth looking into.

Trading up. Apex/Expo and Nepcon China certainly showed vast improvement this year. Numbers were up at both shows, a reflection of the improving economy and (somewhat) open checkbooks. Especially noticeable at Apex/Expo was how engineers filled the floor through the third day: I would need a good miner to dig up a memory of the last time that happened. China’s rebound is not so much of a surprise, though it will be interesting to see how much longer that show lasts in the city when the Chinese government is doing all it can to push manufacturing out of Shanghai. And while the bloom is off the rose in Las Vegas, Apex at least demonstrated that North America can for now handle an annual event. (See our full report here.)

Dying dinosaur. The above notwithstanding, if you took $100,000 in cash and several thousands more in time and travel expenses and spent it trying to convince a handful of potential customers to buy your product, sometimes without even bothering to turn that product on, you would be hard pressed to convince an outsider this is a good way to run a business.

Yet, that is exactly what an SMT equipment trade show has come to represent.

That $100,000 – which is hardly a conservative estimate, as freight and hall drayage costs often reach $25,000 for a single placement machine, and many equipment OEMs bring several lines to a single show – would be much better spent sending potential customers plane tickets and picking up hotel accommodations for onsite visits to the suppliers’ demo rooms. After all, at a typical show today, few machines are operating in anything more than dry runs, and many aren’t plugged in at all. They are giant pet rocks. Kicking the proverbial tires is all a customer can do.

Equipment trade shows in our industry are not sustainable. Investing in their survival means spending thousands to chase hundreds. It’s a faulty premise, and it is only a matter of time before this dinosaur goes extinct.

Changes. A warm welcome to Bekah Just, our new production manager, and a sad, sad goodbye to the absolutely unflappable Katie Haddox who, after 12 years with UP Media (and 10 working with me), is leaving to explore California with her two dogs. Each month, Katie’s slim shoulders moved mountains to get the issue designed, laid out, printed and distributed. I wish her the best of luck, and I will miss her tremendously.

Mike Buetow is editor-in-chief of CIRCUITS ASSEMBLY; mbuetow@upmediagroup.com.

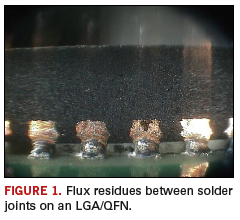

Undissolved flux can leave a mess under low-standoff parts.

Figure 1 shows a side view of solder joints on an LGA/QFN package. Between the terminations, evidence of flux residues is visible and would be common on a standard assembly process. Flux residues are also visible under the package.

(The typical standoff height of these packages is below 0.004˝. The example here has a standoff height of 0.008˝.)

Looking at the flux residues, it is suggested the cleaning process has not been correctly or completely reviewed. The residues look to have been through a cleaning process and are not being dissolved, or are insoluble due to poor process compatibility. A proper evaluation of the process, paste, cleaning system and chemistry needs to be conducted to confirm the residues are compatible and the cleaning system is capable of cleaning the component standoff height on this LGA/QFN package.

Dr. Davide Di Maio is with the National Physical Laboratory Industry and Innovation division (npl.co.uk); defectsdatabase@npl.co.uk. His column appears monthly.

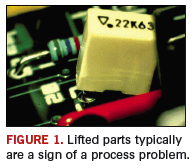

If parts are coming off the board, check the conveyor speed and lead lengths.

When components show lifting during wave soldering, the following mitigation steps might prove helpful.

Primary process setup areas to check:

- Conveyor speed too fast. Slowing the conveyor will increase the immersion time in the wave and overcome thermal mismatch or demand.

- Incorrect lead length: Shot leads may shift and can pop out of the hole.

- Board flex or warpage.

- Other things to look for in the process:

- Solder wave height too high.

- Conveyor vibration.

- Board incorrectly seated.

- Solder wave uneven.

- Conveyor angle too high.

- Defective fixture.

- Excess flux blow-off.

- Early removal of board.

Other things to look for with the assembly:

- Improper board handling.

- Component lead length too long.

Things to look for with the board design:

- Poor pallet design.

Paul Lotosky is global director - customer technical support at Cookson Electronics (cooksonelectronics.com); plotosky@cooksonelectronics.com. His column appears monthly.

Eliminating waste through Lean principles means balancing tradeoffs.

Practitioners of Lean manufacturing are familiar with Taiichi Ohno’s seven deadly wastes: overproduction, waiting, transportation, inappropriate processing, unnecessary inventory, unnecessary or excessive motion and defects. While focusing on waste elimination in each of these areas is desirable, often dealing with production realities means tradeoffs must be made.

As a result, reducing costs by improving efficiency drives manufacturing and quality engineers to become combinations of risk analysts, strategic planners and coaches. This is because all wastes tie into one another and reducing one may fix others. So, the most effective Lean strategies look at the overall organization and the way each action impacts other actions. A robust Lean program emphasizes to each employee that customers include both the party receiving the product and the person who touches a product after they finish processing it. The result is an organizational culture that focuses on improvement, but also recognizes constraints.

Cause and effect. Nowhere are constraints more evident than in the electronics manufacturing services environment. Even when customers are targeted based on their maturity in Lean practices, variations in forecasting, processing and supply chain are introduced with every new customer. This month, we look at each of the seven wastes and likely tradeoffs that must be considered. We also look at practices EPIC has found successful in achieving balance between Lean best practices and the reality of serving a diverse customer base.

Overproduction is a waste typically driven by inefficient processes and as such, it often reflects elements of the other six wastes. Overproduction results when inefficient processes drive higher scrap levels or shortages, and production output is increased to ensure demand is met. Automation is one way to increase production efficiency and quality, but EMS automation strategy needs to be flexible to support likely variations in product configuration and demand. Higher levels of automation can also drive higher cost, so the “perfect” level of automation may never be achievable. Plus, automation is only half the equation. Preventive maintenance and calibration are important in ensuring repeatable processes, as equipment that fails or is out of spec will add bottlenecks or defects. Smaller lot sizes can help minimize overproduction, but every changeover introduces an opportunity for failure and decrease in operational efficiency.

EPIC’s model looks at automation strategy carefully. Equipment and process variation is minimized. The same platform is used in all facilities, so improvements made in one facility are easily transferred. Specialized wave solder equipment and vapor phase reflow are used to create a broader process window that either permits automated changeover or doesn’t require any change between products. All SMT lines are identical. There are no specialized topside or bottom-side lines.

Production personnel are cross-trained in multiple processes so they can move between processes based on demand patterns. Smaller lot sizes can be processed with minimal changeover impact, and demand variations driven by multiple customers are accommodated with minimal waste of resources or bottlenecks. Design for manufacturability/testability (DfM/DfT) recommendations help guide customers toward practices that better utilize production resources and minimize defects. The effect is minimized overproduction.

Waiting is a simple waste. Products in wait state at any point in production are essentially stagnant money merely sitting on the floor. Increasing throughput by processing in smaller batches converts waiting to free cash. However, elimination of waiting is achievable only if material is available. A single, inexpensive passive component delay can halt a production build, negatively impacting inventory turns and cash flow.

EPIC’s system typically processes product into finished goods within 48 to 72 hr. Material bonds are established and buyers are focused not on ordering to JIT demand, but on managing exceptions down the pipeline. The result is the ability to identify potential material shortages with long enough lead-time to address the issue. The DfM/DfT discipline, broader process windows and smaller lot size philosophy described above also contribute to reduced bottleneck potential and an overall reduction in wait time between processes. The net effect is improved inventory turns, increased cash flow, and improvements to on-time delivery.

Transporting is the waste of excessive movement. Transport waste can be created in many ways. A poorly laid out facility is often the biggest driver of transport waste. However, inefficient automation or too much process segregation can also drive this waste.

Our factories are designed to minimize transport by moving production in a synchronous manner according to general processing requirements. Where possible, multiple processes are combined both to eliminate transport waste and potential defects that can be introduced in isolated processes. For example, in some build-to-order projects’ final programming, test and packing are combined at the test station. This minimizes transport between workstations, eliminates the possibility that varying configurations will be mislabeled, and optimizes process takt times to improve product flow.

Inappropriate processing is waste driven both by lack of DfM/DfT discipline and by lack of sufficient documentation control. This can be a more difficult waste to control in the EMS environment because customers may reject DfM/DfT recommendations, and robust documentation requirements can create bottlenecks.

EPIC’s DfM/DfT system prioritizes recommendations to make it easier for customers to understand how critical each recommended design change is to overall product quality. Documentation control is centralized to make sure production only has access to the most current revision of work instructions. Design travelers accompany each work order to ensure that during shift changes or personnel changes there is a clear trail on what is being processed. Smaller batch sizes also contribute to minimizing this waste.

Unnecessary inventory is also a challenging waste to minimize in the EMS environment. Unnecessary inventory comprises raw material, work-in-process and finished goods inventory. While smaller lot sizes can minimize WIP, the relationships with customers found in EMS means forecasting and supply base choices are often a compromise between customer preferences and Lean best practices. Economy-driven variable demand further tests the system.

In the EPIC model, the program manager starts by developing the customer order replenishment methodology. The tool for determining visibility into the customer’s demand is defined (i.e., ERP, EDI, etc.), and replenishment “pull” signals are defined.

Once these issues are addressed, initial finished goods kanban bin sizes are established. Trends are analyzed and bins resized as appropriate with customer approval. Strategic suppliers produce to the MRP forecast and ship to EDI release signals. Consignment, in-house stores and vendor managed inventory programs are used with strategic suppliers to maintain buffers closest to the point of use.

Pipeline status or “bond” reports are regularly reviewed with supplier teams to ensure buffers and replenishment streams are able to support planned production within a range of variation based on past historical demand, current forecasts, customer service lead-time guarantees to their end-market, manufacturing lead-times and transit lead-times.

Like the wastes of transport and inappropriate processing, unnecessary or excessive motion costs money and slows throughput. And, as with the waste of inappropriate processing, customer reluctance to implement DfM/DfT recommendations can be a constraint in improving efficiency.

EPIC’s automation strategies, DfM/DfT process and focus on designing factories with sequential processes all help improve efficiency, but ultimately, the most success in reducing this waste comes when customers are willing to adopt DfM/DfT recommendations. Engaging the EMS provider during the design stage ensures optimal process efficiencies, translating to a successful and cost-effective product launch.

Excessive defects represent both the seventh waste and a byproduct of most of the other wastes. They drive unnecessary inventory and overproduction. However, completely eliminating defect opportunities carries a high cost, and most EMS providers make tradeoffs to minimize defects while aligning with customer cost goals. Other defect minimization practices include:

- Eliminating non-value-added activities.

- Minimizing touch labor.

- Maintaining a well-trained workforce.

- Using Six Sigma tools to analyze root cause of defects.

- There is no one right formula for eliminating any of these wastes. The best course is developing a strong production framework with processes that accommodate the bulk of customer requirements, and fine-tuning as required.

Ryan Wooten is engineering manager at EPIC Technologies (epictech.com); ryan.wooten@epictech.com.

Press Releases

- Distron Adds Second Shift, Expanding Capacity to Support Around-the-Clock Production

- Horizon Sales Expands Consumables Portfolio with ROCKA Partnership, Bringing More Value to U.S. Manufacturers

- Libra Industries Appoints Gustavo Sariñana as General Manager of Guaymas Facility

- BTU International Appoints Performance Technologies Group as Exclusive Representative in Tri-State Region