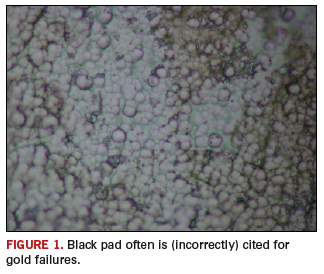

Many gold failures are incorrectly attributed to black pad issues.

Figure 1 shows the surface of a nickel pad on a printed board after stripping the gold from the nickel surface. The image shows limited evidence of corrosion on the nickel surface at the grain boundaries on a bare board. Some evidence of gold is also still visible. Solder joint failures when examined normally show far more corrosion around the nickel boundary. Much debate centers around the subject of black pad. Changes to nickel chemistry and better control have reduced solder joint failures.

Unfortunately, many gold failures are attributed to black pad issues, when clearly they are not. Close cooperation is necessary with the PCB supplier and its chemistry supplier to determine the cause of the problem. Always ask to review the chemistry supplier’s audit reports conducted at the PCB supplier’s offices. Independent analysis also may be required, if the assembly processes are considered the root cause of any joint failure. Review the PCB fabrication process, the reflow temperature and time in a liquid state for the solder paste.

These are typical defects shown in the National Physical Laboratory’s interactive assembly and soldering defects database. The database (http://defectsdatabase.npl.co.uk), available to all this publication’s readers, allows engineers to search and view countless defects and solutions, or to submit defects online.

Dr. Davide Di Maio is with the National Physical Laboratory Industry and Innovation division (npl.co.uk); defectsdatabase@npl.co.uk. His column appears monthly.

Vibrations can weaken the solder joint.

Rough or disturbed solder is a solder fillet that solidified while one or both metals to be joined were vibrating. The result is a weak, non-uniform metallic structure with many micro-cracks.

Primary process setup areas to check:

- Check conveyor for vibration or “jerky motion.”

- Removal of the board prior to the solder solidifying.

Other things to look for in the process:

- Solder temperature too low.

- Conveyor speed high.

- Solder wave height low.

- Conveyor vibration.

- Solder wave uneven.

- Early removal of board.

- Solder contaminated.

- Board not seated right.

- Excessive solder dross.

- Flux applied unevenly.

Things to look for with the board design:

- Poor pallet design.

Paul Lotosky is global director - customer technical support at Cookson Electronics (cooksonelectronics.com); plotosky@cooksonelectronics.com. His column appears monthly.

Characterizing the measurement system reduces results variance.

Before starting an optimization process, be sure the measurement system is accurate and precise. Accuracy is defined as absence of bias in the measurement and precision as the dispersion of the measurements. To quantify precision, a gauge study can be used. Sources of dispersion are failure of the measurement instrument or gauge to exactly repeat itself (repeatability) and failure of the operator or machine to exactly reproduce the measurement technique (reproducibility). The Reproducibility and Repeatability (R&R) gauge study is defined as1:

s² Equipment + s² Appraiser = s² Total (R&R)

In an experiment or optimization process, a number of samples are measured multiple times by different people. If the gauge is not precise, the measurement of the process is not real and could falsely indicate the process is off target. In this case, action is required to reduce the variance. The corrective actions include better instrumentation, operator training programs, or both1.

Typically, 20 measurements are taken. If the experiment takes a long time or is expensive, a number of 10 to 15 is also acceptable. To assess gauge capability, the precision-to-tolerance (P/T) ratio is used:

P/T = 5.15 s Total (R&R) / (USL-LSL)

where 5.15 s is a commonly used number containing 99% of the theoretical distribution.

Some use a 99.7% interval (Six Sigma). USL and LSL stand for upper specification limit and lower specification limit.

When P/T < 0.10, the measurement system is good and acceptable; when P/T is between 0.1 and 0.3, the measurement system is just acceptable; and when P/T > 0.3, the measurement system is not acceptable. It is possible to set the P/T threshold at any proportion realistic to the process measurement needs.

Here’s an example of gauge R&R to measure amount of flux in a wave soldering process. The amount of flux sprayed on a PCB should be consistent. If the flux amount is less than specified, the number of defects (bridging, spikes, solder balls) could increase. If the amount is too high on the assembly, the flux residues are exceeding the limits and may result in electromigration.

The consistency of the spray system can be measured by spraying the flux into a cup and measuring the amount of flux on a scale. In this experiment, an assembly is fed into the solder machine, but instead of spraying the flux on the board, the flux is collected in a cup. This is repeated twice for 10 different boards. Three different appraisers followed this procedure, resulting in the following data expressed in grams (Table 1).

From these results, the P/T is given by

![]()

P/T = 5.15(0.326661)/10 = 0.1682

Based on this information, spraying flux in a cup and weighing the amount is an acceptable method. This statistical method can be used in several applications: measuring solder paste volume, flux amount, wave height, profiler performance, and so on.

Reference

1. W. Kolarik, Creating Quality Process Design for Results, McGraw-Hill, 1999.

Ursula Marquez de Tino, Ph.D., is a senior process and research engineer. Her column appears monthly.

Selected results from a study on registration using closed-loop control.

As we noted in March 2009, closed-loop process control can be defined as a system that continually monitors and adjusts a process to maintain a particular target value of an output or outputs (Figure 1).1 To improve the performance of positional accuracy, we tested a closed-loop system that uses a CyberOptics SE300 SPI to measure X, Y and ∆ print offset (Figure 2). This information is then passed to the printer to make appropriate corrections to the print offset, as necessary.

To evaluate the performance of the closed-loop control, three tests were conducted:

- Evaluation.

- Baseline.

- Long run.

Evaluation tests. The objective here was to evaluate the performance of the closed-loop controller interface and acceptable range of correction factor application. Correction factor is defined as the percentage of SPI-measured offset value applied to the next board in the printer. The primary function of the controller is defined here as to adjust the print registration for each squeegee direction until it reaches the target value. This test was conducted using a standard Speedline test board (254 x 203 x 1.575 mm, four-layer FR-4 board with ENIG surface finish). The test vehicle is divided into four quadrants with the same pad layout in each quadrant (Figure 3a). The top half of the board is a “step and repeat,” while the bottom half is the mirror image of the top. Each quadrant incorporates a range of commercially available components and packages (Figure 3b). The print test was run on 40 boards for statistical confidence in the results.

A gauge study on the SPI machine was conducted before the start of the study to ensure the SPI was repeatable. For the gauge study, one board was inspected 15 times (Figure 4). The range for the 15 boards was measured to be less than 5 µm for X, Y offset and 0.002° for ∆. This was considered to be acceptable. Based on these results, the X, Y offset specification was set to be +0.05 mm.

Baseline test. The objective of this test was to baseline the print process without the presence of closed-loop control. The test was performed for 100 boards using a commercially available Type 4 Pb-free paste. The board used was a commercial cellphone board, with four boards to a panel. (Due to the proprietary nature of the product, the actual image of the board is not shown. Instead, a representative schematic is shown in Figure 5.) The board was 191 x 117 x 1 mm with OSP finish. Four areas on the board were chosen to be monitored for X, Y and ∆ conversance, as shown in the enclosed white boxes. At the beginning of the test, an operator using visual methods aligned the board to the stencil. Once optimum alignment was achieved, the process was run for 100 boards without any alignment tweaking.

Long run tests. The objective of this test was to evaluate the stability of the controller for long manufacturing periods (i.e., to simulate a production condition). The test evaluated the ability of the controller to maintain the print process close to the target registration value, and check for rapid convergence. The target for this test was zero offset. The same cellphone board was used for the long run test.

Next month: the results.

Rita Mohanty, Ph.D., is director advanced development at Speedline Technologies (speedlinetech.com); rmohanty@speedlinetech.com.

The right methodology will go a long way toward reducing defects.

Temperature controls on different soldering processes always have to be monitored, and due to the quantity of factors that take place in wave soldering, it is in this process where thermal control becomes indispensable. Whether the assembly is simple (single-sided PCBs populated with conventional components) or complex (double-sided PCBs populated with QFPs, BGAs, etc., on both sides), it is important to monitor several parameters in order to obtain acceptable, reliable solder joints.

Before setting the profile (Figure 1), check that the potential process variables are monitored and under control. For example, all the parts to be soldered (the PCB and components to be mounted) must pass solderability requirements according to company standards. Also, check the flux shelf life, the density (for foam fluxers units), and the quantity and penetration.

The solder pot measurements must be taken and contamination levels must not exceed established standards. Likewise, the machine itself must be characterized according to established standards. These characteristics include preheat and solder bath temperatures, conveyor speed, wave heights, contact time and parallelism. Several soldering profiling devices can help extract all these technical data.

Profile considerations. As in the reflow process, every product has its own thermal profile. The thermal profile’s features will be determined by several elements:

The flux type, and the time and temperature to completely evaporate the solvents and achieve optimum activation. For Pb-free applications, due to the slower wetting and higher temperatures, the flux must offer sustained activity and a higher thermal activation point.

The wave configuration. Depending on the product, different configurations will be used. For example, for Pb-free applications or products with high thermal mass, it is recommended to raise the contact time to increase thermal transfer. To maintain the same throughput (same conveyor speed) and preheat ramp, according to manufacturer requirements, it is necessary to use special nozzles that provide a higher contact time. Preheat module configuration is another issue. Zones with top and bottom preheat areas will increase the board assembly temperature without increasing the bottom-side preheat and overstressing the flux.

The solder frame. This input is included in our thermal profile due to the thermal absorption of the material and the so-called shadow effect in areas close to the components to be soldered.

When soldering problems because of high thermal dissipation in the assembly are encountered, could the thermal profile be increased as needed to achieve these requirements? Not without compromising product reliability and adding to the potential for product failure. In such cases, review the product design or PCB substrate characteristics, and change the chemistries and solder materials, processes or equipment, if allowed.

Creating the profile. To obtain the profile, a sample coupon is needed. An assembled coupon is recommended, if possible, to most closely simulate the thermal response of the actual assembly.

Next, the thermocouples will be connected to the through-hole components to be soldered (Figure 2). If used, the solder frame will protect the components. Ceramic chip capacitors will be placed on the bottom to control for thermal shock.

To obtain data, thermocouples are connected to the profiler; the equipment is turned on, and the board and profiler are run through the wave. When the board exits the machine, the data are downloaded by the software application.

With those data, the preheating ramp, temperature prior to the solder bath, thermal shock, contact time and cooling ramp can be analyzed. At the same time, soldering requirements like wetting or solder fill will be validated.

Common and uncommon problems. During profile development, it is very common to find solder defects such as opens, shorts or insufficient solder fill. However, other harder-to-detect issues can be uncovered, such as cracks in ceramic components (Figure 3) and undesired reflow on topside components. Cracks from excessive thermal shock (Figure 4) can form and can cause variation during operation or internal shorts. Undesired reflow is due to an excessive temperature on the top of the PCB and can cause component misalignment or variation in solder joint properties.

It is necessary to understand the importance of temperature control in all the processes, mainly in reflow and wave. To find the root cause of some board failures can become very difficult and, of course, the cost of repair can become a problem too. With a good thermal profiling methodology, this cost could be saved or reduced significantly.

Francisco Anaya is a process engineer at Celestica (Valencia) (celestica.com); fjaosa@celestica.com.

A trip through Zestron’s tech center in Germany reveals a company dedicated to fixing process problems.

With the advent of no-clean fluxes and solder pastes, the need for cleaning electronics assemblies disappeared.

Or so some would have you think.

But while the masses switched, ahem, en masse, to no-cleans, often in hopes of eliminating what was widely seen as a non-value-added step from the assembly process, a not-so-funny thing happened: Field failures and legislation.

The influx of no-clean coupled with better process control drove the use of cleaning to general consensus of 5% of all boards, mostly for high-reliability applications such as military, certain telecommunications, and aerospace. But the broad switch to Pb-free solders, prompted in large part by the RoHS Directive, and more densely packed boards that effectively turn even trace residues from aesthetic nuisances into potential hazards, has brought about a renaissance for cleaning advocates. And to a degree, suppliers of cleaning materials are, well, cleaning up.

Zestron, one of the perhaps two best-known providers of cleaning chemistry, estimates it has installed more than 1,500 processes worldwide. The company, which has developed several versions of aqueous- and surfactant-based cleaners, plus a line of vapor recovery systems, credits the litany of legislative protocols and directives for having a significant impact on the industry’s approach to soldering. “We’re definitely seeing an increase in cleaning,” says Mark Cherubin, group head of marketing for the Ingolstadt, Germany-based firm. “RoHS, then REACH: The various trends are pushing the issue.”

Launched outside Munich in 1975 by Dr. Oskar Wack, Zestron has grown into a multinational corporation with facilities in the US, Shanghai, and its newest site, in Kulim, Malaysia (sidebar). The company focuses its electronics cleaning efforts on semiconductors and SMT. Last year, Dr. Wack turned over the day-to-day operations management to his son, Harald, who is based at the company’s Manassas, VA, site. (See “New Zestron Global HQ Takes Flight,” Circuits Assembly, June 2007.) (It also has a business unit for automotive cleaners, which Dr. Oskar Wack still oversees.)

At its main campus, about 60 miles north of Munich, Zestron last fall opened a new 30,500 sq. ft. facility, featuring a state-of-the-art, 9,000 sq. ft. analytical and technical center said to be the largest in Europe. The center, which Circuits Assembly visited in November, features a host of testing equipment, including a Gen3 cleanliness tester, Keyence digital microscopes, a Metronelec CT 100 ionic contamination tester, a climatic chamber, and an array of other gear for testing chemicals, surface energy, SIR and more from ThermoFisher, Dataphysics, and other leading suppliers. Adds Cherubin, “We will also work with external labs, as customers wish.”

Inside the technical center is a sea of cleaning machines: spray, inline, batch, you name it, some 30 in all, from a variety of well- and lesser-known suppliers. Walking through the center is “like looking for a car,” jokes Cherubin.

It only seems every make and model imaginable is available. In fact, Zestron prefers to site machines that are typical of what each region’s customers use. For example, in the US, where cleaning tends to be inline, the company has Speedline Accel and Aqueous Technologies machines.

Asked why Zestron doesn’t standardize on a small number of lines, Cherubin responds, “The problem for users [trying to compare cleaning materials] is it’s time-consuming and there is no neutral opinion. This way, we work with all equipment manufacturers, commission-free, and we can give an independent point of view.”

Working with customers, Zestron’s process engineers will narrow the choice to two or three machines, run trials, and provide written reports that outline the expected results in a customer’s factory. Trials are run for between 500 and 600 customers each year, Cherubin says.

Over in production, batches are produced on a pair of semiautomatic, palletized lines capable of producing 15,000 units per shift. Computer-controlled, two-story-high mixers – one two tons, the other five tons – provide ample mixing capacity. Raw materials are vendor-managed. Lots are sampled for traceability, with samples stored for three years.

Responsible for product development is a group that features three Ph.D.s and over 20 members of lab staff. To provide customers with close process support and to help to find the most suitable cleaning process, a team of 16 process engineers are available. Staffing is similar at its 15,000 sq. ft. technical center in Virginia, while the roughly 4,000 sq. ft. Shanghai site has nine staff overseeing a pair of inline and batch cleaning lines and a small analytics lab.

Engineering and R&D stay connected through weekly video conferences, and R&D is coordinated monthly, at which time product development is reviewed and product managers at each site discuss their latest trials.

Customers and prospects are provided with an array of training opportunities, with monthly seminars on topics ranging from coatings to surface analysis, and (of course) PCB and stencil cleaning. “We want to show the different things we have. Most [attendees] will bring part with them, and we show them how we can help,” says Cherubin.

The company has found getting through to designers problematic, however. Says Cherubin, “We have found it’s very difficult to teach designers about design for cleaning. Companies as a rule try to avoid cleaning: It’s an extra step and extra cost. In principle, it’s very difficult to incorporate cleaning at the design level.” Instead, he adds, it falls to Zestron to try to resolve cleaning different geometries that are on the board.

While taken for granted in most corners – after all, washing is one of the first things we learn as children – the technical challenge of cleaning circuit boards can be mighty. Even no-cleans leave residues of varying degrees (although, somehow, a US patent was issued in 2004 for a residue-free solder paste), and some solder suppliers have taken to calling their materials “cleaning friendly.” Says Cherubin, “For a high-precision business, there is no such thing as ‘no-clean.’ ”

Even conformally coating the board won’t ensure the residues remain trapped and benign, Zestron says. “Flux residues left after the soldering process can cause delamination of the coating. Additionally, due to their hydroscopic nature, they can pull humidity through the coating, causing electromigration and ultimately leading to field failures of the boards,” Cherubin explains.

Today’s boards feature low-standoff components such as µBGAs, flip chips, and 01005-sized passives, and short reflow profiles can cause flux entrapment and voltage leakage.1,2 This development is the latest reminder that, for the time being, the component technology is advancing faster than process technology. At home in its new technical centers, Zestron is well situated to aid manufacturers looking to close that gap.

References

1. Terry Munson, “Stray Voltage on Low Standoff Components,” Circuits Assembly, April 2006.

2. Terry Munson, “Let It Flow,” Circuits Assembly, December 2005.

3. Malaysian Industrial Development Authority website, mida.gov.my/en_v2/index.php?page=ee, January 2010.

Mike Buetow is editor-in-chief of Circuits Assembly (circuitsassembly.com); mbuetow@upmediagroup.com.

Press Releases

- Koh Young Announces Two Sales and Service Changes to Strengthen its Customers in the US and Canada

- Express Manufacturing, Inc. (EMI) Promotes David Vue to Lead Military and Aerospace Division

- SP Manufacturing Expands into UK Avionics Sector, Secures First Customer Engagement

- Kodiak Assembly Solutions Strengthen Domestic PCB Supply Chain Amid AI-Driven Market Pressures