Poor plating can be a culprit, and audits are in order.

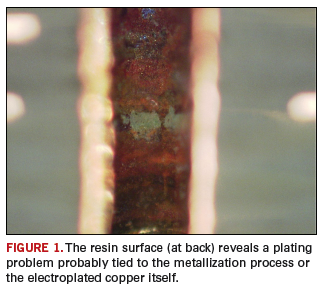

This sample via hole (Figure 1) has been mounted in resin and microsectioned to look at the plating quality. The optical image clearly shows the resin surface at the back of the hole. This is a through-hole plating problem, and closer examination of the plating is required. The center of the sidewall may show the problem relates to the initial metallization process or the electroplated copper. The poor coverage in this example could have been caused by residues on the surface of the drilled hole that were removed during plating. Or, it could be related to a gas bubble in the hole during plating. In the case of less obvious examples, a light is put behind the microsection to show up the degree of laminate coverage.

Auditing the printed board fabrication process with samples examined from drilling through the final copper plating process should be considered. Optical examination of hole coverage and microsections should illustrate satisfactory process control.

These are typical defects shown in the National Physical Laboratory’s interactive assembly and soldering defects database. The database (http://defectsdatabase.npl.co.uk), available to this magazine’s readers, allows engineers to search and view countless defects and solutions, or to submit defects online.

Dr. Davide Di Maio is with the National Physical Laboratory Industry and Innovation division (npl.co.uk); defectsdatabase@npl.co.uk. His column appears monthly.

Solder mask prevents bridging, but poor processes can undo that.

Solder on the mask can occur on solder resist, board surfaces, pallet surfaces and conveyor fingers.

Primary process setup areas to check:

- Poor flux application.

- Flux and resist incompatibility.

- Poor cure of the solder mask.

- Preheat temperature too high.

- Solder temperature too high.

Paul Lotosky is global director – customer technical support at Cookson Electronics (cooksonelectronics.com); plotosky@cooksonelectronics.com. His column appears monthly.

General guidelines for SnPb and Pb-free alloys.

Increased PCB complexity and component density make selective soldering a popular technology, especially when the ratio between surface mount and through-hole components is high. As a replacement for hand soldering or wave soldering with pallets, selective soldering offers many lead-time and solder joint quality advantages. The selective soldering process has unique factors related to the machine design. To develop a robust process, PCB design plays a key role.

PCB or pallet dimensions. The maximum dimensions depend on machine type. The maximum is 610 x 610 mm, while the minimum is 100 x 150 mm. For smaller PCBs, pallets should be used.

PCB warpage. The tolerance for PCB warpage is less than 1% of the PCB diagonal dimension. In a single wave selective process, additional supporting or vacuum pins can be used to control warping. Machines that use multiple waves can handle slightly more warped PCBs due to compensation mechanisms on the plate.

PCB weight and distribution. The maximum PCB weight, including the PCB gripper and pallet, is 15 Kg (33 Lb). In addition, the maximum weight concentration for a particular area for a 100 mm2 or larger PCB must be limited to 1 kg.

Edge clearance. The edge clearance on top and bottom of PCB must be 3 mm. This clearance is necessary to support the PCB on the chain conveyor and the clamping fingers of the PCB gripper.

It is possible to use edge components, as long as there is enough free space to support the PCB. The distance between edge components and the PCB corner should be 28 mm to provide enough space for the clamping fingers of the PCB gripper and position pins. The number of clamping fingers should be sufficient to prevent board warping, and the distance between edge components where the clamping finger will be placed should be at least 26 mm (the width of clamping fingers).

Cutout areas of supporting edges may affect the PCB handling on the pin-chain of the conveyor system. It is recommended to provide breakout parts for such areas where breakout parts can be removed after assembly.

Positioning holes. Two position holes are preferred for precise board positioning. Preferably, one round hole and one slotted hole should be available on the fixed rail side of the PCB. The slotted hole reduces board bending when PCB expansion/contraction occurs during soldering. Hole diameter should be between 3 and 5 mm. Keep the holes outside the 3 mm edge clearance area and keep a free space of 8 mm diameter around these holes.

Lifting areas. At least four areas of 6 mm diameter on the board bottom along the length of the conveyor direction are required for lifting the PCB from the pin-chain conveyor. These supporting areas are normally within a zone of 10 mm, measured from the PCB edges. The total number of lifting support pins must be selected in order to provide a stable PCB during the lifting operation.

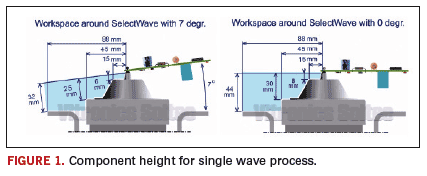

Component height. The general specification for component height on the top side of the PCB is 120 mm. Component height on the solder side is 25 mm for a multiple wave process and between 6 and 40 mm for single wave process. This large range depends on the component position in relation to the soldering area and soldering angle (Figure 1).

Clearance between components and board. There should be at least a 0.5 mm gap between the component body and the pad on the component side. This permits flux vapors to escape and reduces opens. One cause of open joints is flux vapors escaping via the solder side of the PCB.

Lead protrusion. Lead protrusion depends on the PCB type. For single-sided PCBs, the lead length should be at least half the pad size, while for double-sided PCBs where the PTHs are completely plated, the lead protrusion should be at least 25% of the pad size.

When a dip soldering process is used, lead protrusions up to 10 mm can be used. However, when a drag process is used, the lead protrusion can go up to 4 mm to avoid bridging.

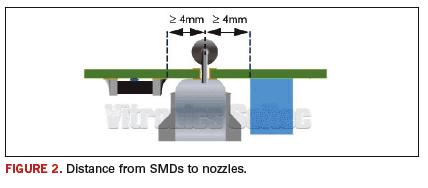

Surface mount devices proximity. Free space around selective soldering joints is necessary to have free access to the nozzle and to reduce thermal load to the surrounding components. In general, a free space of 4 mm should be used. This is measured from the center of the solder joint to the surrounding components/joints. The 4 mm is based on 3 mm (joint to inner nozzle wall) + 0.5 mm (nozzle wall) + 0.5 mm clearance (Figure 2).

When a drag soldering process is used in a single wave process, the free space depends on soldering angle and/or height of the components. In a single wave process, a minimum distance of 1 mm is possible, provided there is sufficient free space at the opposite side of the solder joint for placing the minimum admissible diameter nozzle (Figure 4). For a multiple wave soldering process, the distance can be 2.5 mm.

Gap between nozzles and PCB. When nozzle plates are provided with standoff pins, the pins will keep a gap between PCB and the top of the nozzle at a fixed distance. The distance can be between 0 and 1.5 mm. The most common gap is 0.3 mm.

These are general guidelines to consider when designing a PCB for a selective process. These recommendations will ensure minimum defect process when the optimal process parameters are used. For specific applications, contact Lammie Willemen (lwillemen@vsww.com) or Chris Curole

(ccurole@vsww.com).

Ursula Marquez de Tino, Ph.D. is a process and research engineer at Vitronics-Soltec, based in the Unovis SMT Lab (vitronics-soltec.com); umarquez@vsww.com. Her column appears monthly.

Embedded passives are inevitable, and fabricators must be brought up to speed.

There comes a point in every technology’s lifespan when, either by necessity or mandate (i.e., legislation), evolution must occur. We’ve seen this with the migration from through-hole to surface mount and, of course, the recent transition to Pb-free. One such technology that emerged on the scene more than a decade ago, but never quite got its legs, is embedded passives. Not that there wasn’t interest – there was (and is). A relative few leading-edge firms invested in the technology and successfully employed it, but for commercial reasons (and in some instances, patent issues), it was not implemented. Now, however, it seems there is a renewed interest in the technology, largely due to miniaturization requirements. Like SMT many years ago, it appears embedded passives may be the industry’s next leap of faith.

For those unfamiliar with embedded passive processes, I’ll attempt to explain the basic parameters. In theory, it’s a pretty simple concept. At the board fabrication level, a thick film, resistor-based ink, is applied to the various PCB layers using high performance screens and screen-printing equipment. So, instead of having numerous traces that would traditionally have led to resistors on the top or bottom layers of the board, you are now able to locate them on the individual copper layers. The material is printed to a designated area within the layers and then repeated on each layer as required. The key to success is ensuring the tolerances of the prints are within a given range – usually +/-10%. Traditionally, the resultant embedded passive requires a post process (laser trimming) to guarantee the required tolerance. That said, the accuracy of today’s printing systems and the ability for them to verify deposit volumes enable significant reduction – if not outright elimination – of any laser trimming requirements. In fact, our company conducted a series of evaluations on this process and has shown repeatable printing with +/-10% tolerance can be achieved. I’d even take that one step further and say, with a combination of a leading-edge screen printer and well-manufactured screens, a +/-5% tolerance capability should be achievable.

Anything less would likely require laser trimming.

Personally, I think some of the reluctance on the part of fabricators is they are simply unaware of the capabilities of today’s printers. In fact, I know this is the case, based on comments I’ve heard at technical sessions. If board fabs are willing to invest in the tools needed for today’s embedded passives, they can successfully implement this technology.

Rest assured, embedded passives are coming. With the onslaught of 01005s and the next chipset after that, there is going to come a point when miniaturized passives simply cannot be placed or repaired. There is a finite size at which components can be placed at the speeds required, and this barrier will force embedded passives to the fore.

For the assembler, embedded passives are nothing but a win. When you consider nearly 25% of the solder joints on a PCB are for passives and up to 50% of those are resistors (which are likely the passives that will go embedded first), consider all the advantages this technology provides. The board comes pre-loaded. That means placements you don’t have to do; imagine the time saved and throughput achieved by eliminating this from the process. Then there’s the real estate factor. By freeing up the space previously allotted for passives, additional functionality can be added. Statistics also show the reliability of embedded passives to be much better than that of conventional passives. Because they are encapsulated within the layers, these components are less susceptible to shock damage from drops and vibration, as well as more protected against humidity and its ill effects.

Last but not least, embedded technology permits faster clock speeds because they can be placed in a three-dimensional location – the passive device can be placed directly under the chipset; this makes for smaller trace lengths, which enables higher frequency signals to be processed. Consequently, embedded technology is a key enabler to the smaller, faster and lighter paradigm.

For embedded passive technology, it’s not a matter of if, but when. It’s a leap of faith we will all take together and, if your PCB fabricator invests in the right systems, the leap will likely result in a very soft landing.

Clive Ashmore is global applied process engineering manager at DEK International (dek.com); cashmore@dek.com. His column appears bimonthly.

Main considerations for incorporating test in a board design.

In our experience, there is a general lack of awareness about what needs to happen at the design level to increase the testability and overall test coverage of a finished assembly. This issue is straining the customer/supplier relationship, because it goes beyond what the supplier independently can provide without customer input and consideration during design.

What is the basic problem? Suppliers spend millions of dollars and countless labor hours on different quality initiatives aimed at producing zero defects. Yet none has been able to achieve this without one certain element: test!

In design for testability, the test method must be decided prior to finalization of the design. The four main options are functional, in-circuit (ICT) fixture, flying probe ICT, and boundary scan. Each has different design considerations.

ICT with fixtures has been around the longest and is the most widely used. It is particularly well suited for high-volume, low complexity designs, where the (high) cost of fixturing is justified by the volumes. It can test for shorts, opens, capacitance, resistance, inductance and more, depending on the level of test desired. It is fast and cheap (at a price per test level, once the fixture cost has been absorbed). But fixture costs are high and not suited to low volume. Also, test pad sizes must be large (0.030˝ to 0.040˝) and contained on every net of the design to give the fixture access to the board. The large size of the test pads makes this option difficult to incorporate onto high-density designs or designs with BGAs. After all, the main point of going to BGA package styles is to save real estate. Adding large test pads on every net defeats the purpose.

Functional test also is widely used to “exercise” the end functionality of the board. Its intent is to test circuit functionality and, in theory, catch most major defects, be they component-level or manufacturing defects. However, this is not an opens and shorts test. For example, it would not typically reveal wrong values for passives.

Functional fixturing can be tailored to almost any application. It detects problems with the board functionality or component-level failures, depending on the test hardware and software design. The custom design of test hardware and software, by its very nature, makes this option time-consuming and expensive. For many applications, especially quickturn prototypes or products with short time-to-market, this may not be practical. Also, it is likely functional test will not cover as much as 20% of the circuitry, and thus leave vulnerabilities in the finished product. This is why many high-volume, high-reliability customers do both ICT and functional.

Flying probe, like standard ICT, will test for shorts, opens, capacitance, resistance, inductance, etc. But rather than using fixed test probes, it uses robotic test heads. The obvious advantage is greater access to the circuit board, for greater test coverage, without the high cost of fixtures. In addition, it allows a more “forgiving” DfT approach by enabling smaller test pads (0.010˝ to 0.012˝), enabling use of unmasked vias as a test pad, and enabling test of SMT and PTH component leads. In essence, almost all standard SMT or mixed technology boards can now be tested and with relatively high coverage ratios, even though they may not have been designed with ICT in mind. Also, since there are no hard fixtures, the upfront costs are substantially less. It does require custom software test programming, at a typical one-time charge of $1,000 to $2,500, depending on the number of components on the board and the number of different line items on the BoM. The biggest drawback is test speed. It can take five to 60 minutes to test each board, depending on complexity. It definitely is more suited to low- to medium-volume applications. The other drawback is it cannot test BGA pins without specific test pads on the nets leading into the device, and it cannot functionally test ICs or catch cold solder joints.

Boundary scan is one of the most interesting, most powerful and least understood test options. Incorporated into the original design, it allows the user to program and test many of the major devices on the board, including memory and FPGAs. In essence, it allows programming and functional testing of all JTAG-compliant devices purely through software programming, with diagnostic-level reporting that permits fault isolation down to the pin level.

However, take into account during design that it requires a JTAG connector be added to the board, and that this connector be chained together with the JTAG-compliant devices.

It is the only practical option for testing BGAs because it does not require a test point on every net. It is relatively easy to generate the test programs, and thus relatively inexpensive, and comes with a one-time cost. It is fixtureless. It has powerful programming and diagnostic/debugging options both for engineering and manufacturing test departments. It gives the best of both worlds in terms of functional and ICT features.

Since BGA solder connections only can be examined through x-ray, this ability to test the BGA at the manufacturing level becomes critical. X-ray is inspection, not absolute validation. With these tools, the EMS firm can provide real-time feedback to the manufacturing floor to verify oven reflow profiles, all the more critical when processing BGAs. However, it is not capable of testing analog and passive devices.

The best test solution depends on the application and amount of money you are willing to spend. For high-reliability applications, the best solution may be a combination of these options.

Andrew Murrietta is CFO of Murrietta Circuits (murrietta.com); andy@murrietta.com. His column appears bimonthly.

Higher capex and concern over debt and defaults are in the cards for 2010.

Many economists agree we are at the bottom of the downturn, and the outlook for most regions is brighter. Government stimulus spending around the globe is credited for the improvement, but continues to be required to sustain the recovery. Asia, especially its emerging economies, is experiencing recovery faster than the West. The World Bank upgraded its forecast for China’s economic growth for 2009 to 8.4%. The exception is Japan, where many companies seem to be suffering from a “deer in the headlights” syndrome and don’t know which direction to move. In an attempt to improve Japan’s economic situation, its central bank will pump short-term funds into the financial system to improve liquidity. Many economists caution that stronger domestic demand is needed to ensure a sustainable recovery in China, as well as other regions.

Likewise, 2009 has been a tough year for electronics companies, but projections for 2010 are brighter. While the number of exhibitors in SemiCon Japan in December was roughly half 2008’s count, market analysts were optimistic in their outlooks. iSuppli Japan analysts focused on the new phase of the electronics market. High brightness LEDs, power devices, medical, and energy sectors are seen as growth areas. SEMI forecasts equipment spending would increase from $16 billion in 2009 to more than $24 billion in 2010 – closer to the 2008 level of $29.5 billion. While most spending is for wafer processing, the numbers also include test, assembly and packaging.

There are other positive signs for equipment fabs. Goldman Sachs reported that the top four semiconductor foundries’ total wafer shipments increased 14.6% sequentially in the third quarter, to within 3% of the historical peak set in the third quarter of 2008. TSMC raised its fourth-quarter revenue target and reported that 300 mm shipments were solid until November, and that 65 nm lead-time is 12 weeks. TSMC also reported improvements in 200 mm bookings. Goldman estimates that TSMC raised its capex to $2.4 billion from $1.5 billion in 2009, and will spend more than $3 billion in capex in 2010. Chartered and UMC both increased 2009 capex, and Chartered is now part of Global Foundries, which has already announced major expenditures on its new fab in Albany, NY.

The four major semiconductor subcontract assembly and test operations report improvements in utilization and have increased capex above plans at the beginning of 2009. Some companies, including ASE, are reporting revenue growth. While visibility is somewhat limited, the outlook for 2010 is positive.

The market for semiconductor packaging materials, including thermal interface materials, is expected to reach $15.8 billion in 2009 and grow to $20.1 billion by 2013, according to a new study by SEMI and TechSearch International. Laminate substrates remain the largest segment of the market, worth an estimated $6.8 billion globally in 2009.

Bright spots? Advanced packaging remains an industry bright spot. In 2009 the only major package type to show unit volume growth was the wafer-level package (WLP). This package will grow at a compound annual rate of 11.5% through 2013. Growth in flip chip interconnect also shows promise, as many companies convert from wire bond to flip chip in wireless applications.

The green trend also is driving growth in some segments of the industry, as many regions attempt to cut CO2 emissions and improve energy efficiency. There is increased demand for power devices, as companies make improvements to many types of motors used in a variety of applications such as automotive, energy, and trains. LED shipments will grow for applications, including backlights.

Consolidation is expected to continue in equipment, materials and services. In the materials sector, Henkel’s acquisition of National Starch and Chemical’s business units and Dow Chemical’s purchase of Rohm and Haas stand out as mega-mergers. On the semiconductor equipment side, KLA-Tencor purchased ICOS (the European inspection company), and Applied Materials announced the acquisition of Semitool. In Taiwan, Chipbond and IST have announced plans to merge their gold-bumping service operations and assembly services for LCD driver ICs.

Future concerns. While improvements are projected for 2010, spending levels will take time to return to the levels of 2007 and 2008. While some analysts predict the industry will rebound faster than in previous recessions, others cite the continued need for government stimulus programs to boost demand. Concerns remain about events that could derail the recovery. For example, Dubai’s announcement of a potential default on almost $60 billion of debt left many economists wondering if the city-state is a lone event or a portent of more shocks. Regions of concern include Russia and the former Soviet bloc, as well as the US, Japan and Germany, which are contending with large amounts of debt resulting from excessive borrowing, with the oil binge spending in the former, and budget deficits as a result of stimulus spending in the latter.1

References

1. Graham Bowley and Catherine Rampell, “Looking for the Next Debt Bomb,” International Herald Tribune, Dec. 2, 2009, p. 1.

E. Jan Vardaman is president of TechSearch International (techsearchinc.com); jan@techsearchinc.com. Her column appears bimonthly.

Press Releases

- OKI Launches EMS for AI Server Equipment Featuring Proprietary High Heat Dissipation Technology

- ECIA Announces 2026 Executive Conference Core Committee Members

- Arbell Electronics Named Zestron's 2026 Distributor of the Year at APEX EXPO

- The Test Connection, Inc. Adds Creative Electron Prime TruVision X-ray and CT System for Deeper Failure Analysis